Risposta breve :Sono uguali.

Ulteriori dettagli :Per prima cosa, guarda questo post che è molto correlato alla tua domanda.

In questo articolo si dice:

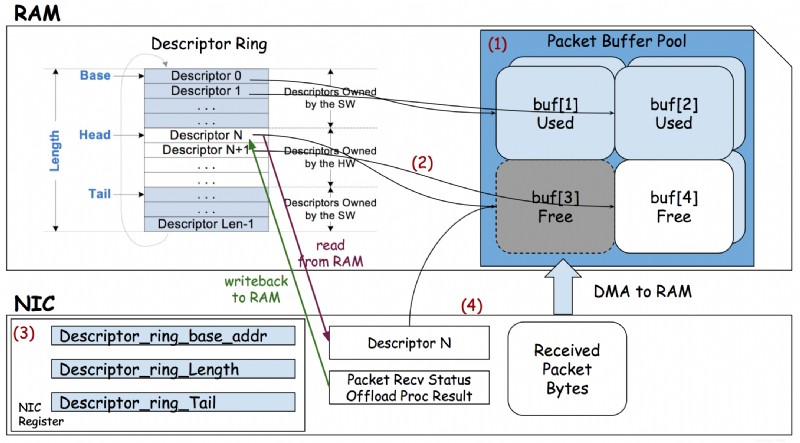

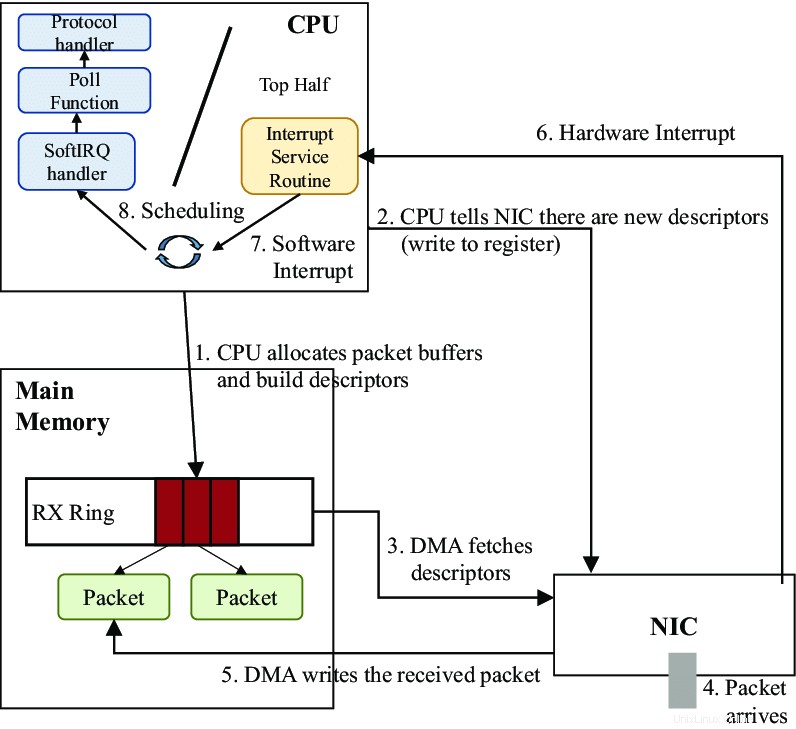

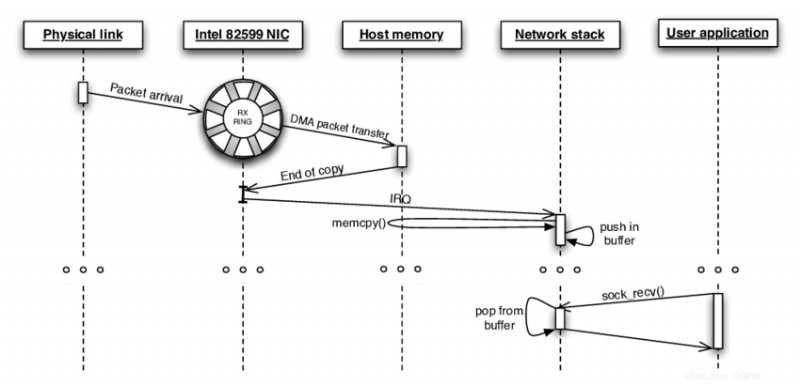

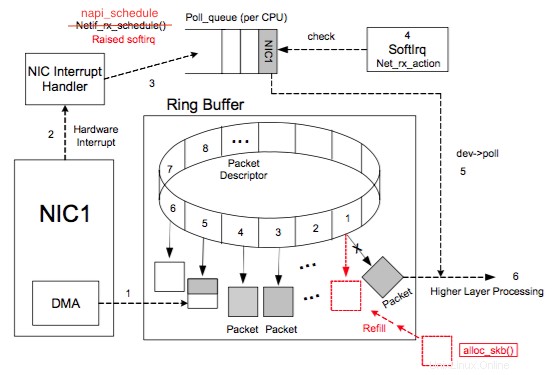

Una variante dell'approccio asincrono è spesso vista con le schede di rete. Queste schede spesso si aspettano di vedere un buffer circolare (spesso chiamato ring buffer DMA) stabilito nella memoria condivisa con il processore; ogni pacchetto in arrivo viene posizionato nel successivo buffer disponibile nell'anello e viene segnalato un interrupt. Il driver quindi passa i pacchetti di rete al resto del kernel e inserisce un nuovo buffer DMA nell'anello.

L'anello DMA consente alla scheda NIC di accedere direttamente alla memoria utilizzata dal software. Il software (il driver della NIC nel caso del kernel) sta allocando la memoria per gli anelli e quindi mappandola come memoria DMA, quindi la NIC saprebbe che potrebbe accedervi. I pacchetti TX verranno creati in questa memoria dal software e verranno letti e trasmessi dalla NIC (di solito dopo che il software ha segnalato alla NIC che dovrebbe iniziare a trasmettere). I pacchetti RX verranno scritti in questa memoria dalla scheda NIC e verranno letti ed elaborati dal software (di solito dopo l'emissione di un interrupt per segnalare che c'è lavoro).

Spero che questo aiuti.

-

Ring Buffer Contiene l'indirizzo iniziale e finale del Buffer nella RAM.TX Ring conterrà gli indirizzi del Buffer nella RAM che contiene i dati da trasmettere.RX Ring conterrà l'indirizzo del Buffer nella RAM dove la NIC posizionerà i dati.

Questi anelli sono presenti nella RAM.

-

Il buffer TX e il buffer RX sono nella RAM puntata dagli anelli TX/RX.

-

Ora il registro della scheda di rete ha la posizione del buffer degli anelli nella RAM .

Ora 1 e 2 possono essere buffer compatibili con DMA, sono chiamati anello DMA TX/RX e buffer DMA TX/RX. Ora, poiché l'anello RX/TX deve rimanere per tutto il tempo, sono realizzati come tipo di meory DMA coerente/coerente. Mentre i buffer sono creati streaming/tipo di memoria Single DMA